# **ERROR CONTROL**

v 2.5 11/April/2024

Based on textbook *Conceptual Computer Networks* by: © 2013-2024 by José María Foces Morán and José María Foces Vivancos. All rights reserved

## **Error Control**

- Bits of information sent in frames may undergo unintended changes as they travel to their destination C) 2014-2018 José Warante ra E006 Viroarcos. All rights ra

- Those changes are known as errors

- Causes of bit errors

- Electromagnetic interference

- Noise

- Electronics faults

### Bit errors

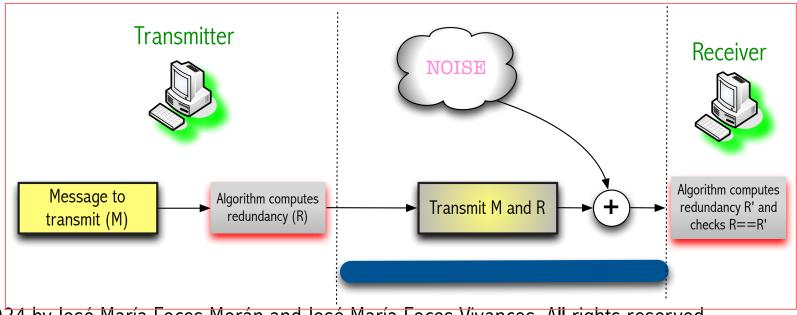

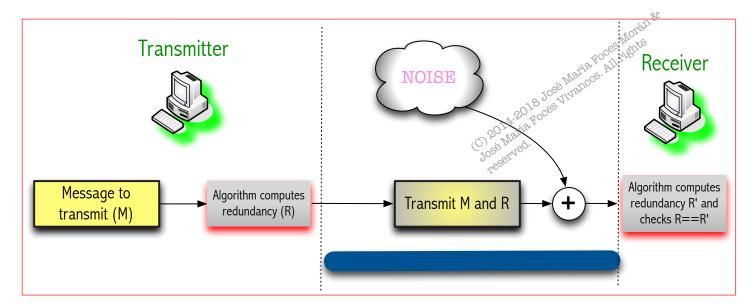

The M bits of information included in a frame are sent along with R bits computed from the M info bits

- The receiver computes R again (R') using the received M bits

- **The receiver checks whether** R == R'

- If true, probably no error happened

- Else, at least one error happened

### Bit errors

🛛 🗆 Error control bits, R

These bits *add* no new information to the message M

These bits are computed from the original message by applying an algorithm known by the transmitter and the receiver

## Error detection and error correction

5

### □ If recipient detects an error, two options:

- 1. Notify the sender to have the frame resent

- ARQ (Automatic Repeat Request)

- Retransmit the frame

- 2. Receiver reconstructs message M by using an error correcting algorithm

- FEC: Forward Error Correction

- Invented originally by Richard Hamming

## **Error Detection**

6

### Common techniques

ParityTwo Dimensional Parity (BISYNC)

Internet Checksum (IP)

IP header, UDP, TCP

CRC (Cyclic Redundancy Check)

Used in HDLC, DDCMP, CSMA/CD, Token Ring

## **Error Detection**

7

#### □ Naïve approach: Transmit two complete copies of the data?

- Identical  $\rightarrow$  No error

- WRONG!

- Unequal  $\rightarrow$  Error

- Extremely inefficient

- n bit message, n bit redundant information!

#### □ Use strong error detection, instead

- Redundancy R of length k bits

- n bits message, k << n</p>

- Example: Ethernet's CRC-32

- Frame can carry up to 12,000 bits of data

- The CRC algorithm requires only 32 bits of redundancy

## Error detection with Horizontal Parity

8

### □ R has a length of 1 bit

- Normally used for 7-bit data (ASCII characters, for example)

- Add 1-bit parity, transmit the resulting 8 bits

- Odd-parity sets the eighth bit to 1 if needed to give an odd number of 1s in the byte

- 7-bit data: 0101010, Odd parity: 0, Send 01010100

- 7-bit data: 0001010, Odd parity: 1, Send 00010101

- **Even parity** sets the eighth bit to 1 if needed to yield an even number of 1s in the byte

- 7-bit data: 1111010, even parity: 1, Send 11110101

- 7-bit data: 1111010, Odd parity: 0, Send 11110100

# Computing the even parity

9

Example:

- $\blacksquare$  M = 7 bits of data

- $\square$  R = 1 bit of redundancy (Even parity)

- **Computation:**

- Parity bit = Data0 XOR Data1 XOR Data2 XOR Data 3 XOR Data4 XOR Data5 XOR Data6

- DATA = 0110110

- **PARITY BIT** = 0 xor 1 xor 1 xor 0 xor 1 xor 1 xor 0 = 0

- Send 01101100

$\ensuremath{\textcircled{\text{C}}}$  2013-2024 by José María Foces Morán and José María Foces Vivancos. All rights reserved

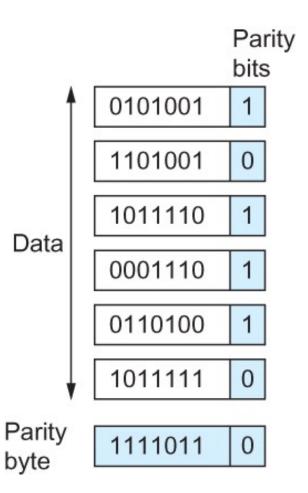

# Two-dimensional parity, an example

10

- Apply parity to each of the 7-bit bytes contained in the frame

- For every 6-BYTE block, compute its block-parity BYTE by computing the parity of each column of bits.

- Two-dimensional parity catches all 1-, 2-, and 3-bit errors and most 4-bit errors

- It's capable of <u>correcting</u> 1 error

# Internet Checksum Algorithm

#### 11

- Not used at the datalink level

- □ Used by IP, UDP and TCP

- Transmitter

- $\square$  R = Add up all the words using 1-complement arithmetic

- Transmit the 1-complement of R (checksum)

- Receiver

- Do the same calculation on the received data

- Compares the result with the received checksum

- □ If data | checksum gets corrupted

- Results will not match

- At least one error occurred

# Internet Checksum Algorithm

12

- Consider the data being checksummed as a sequence of 16-bit integers.

- Add them together using 16-bit ones complement arithmetic (explained next slide) and then take the ones complement of the result.

- □ That 16-bit number is the checksum

13

For protecting frames transmitted on high speed media

The CRC used in Ethernet is 32 bits in length

- Given M, a bit string 110001, for example, we can associate with it a polynomial on a single variable x:

- M(x) =  $1 \cdot x^{5} + 1 \cdot x^{4} + 0 \cdot x^{3} + 0 \cdot x^{2} + 0 \cdot x^{1} + 1 \cdot x^{0}$ =  $x^{5} + x^{4} + 1$

- degree is 5, number of bits is 6

- A k-bit frame has a maximum degree of k-1

- Let M(x) be the Message polynomial and

Let C(x) be a mathematically established Generator polynomial

14

□ Assume M(x)/C(x) leaves a remainder of 0

$\square$  M(x) is sent but, in fact, M' (x) is received

□ The receiver will compute M' (x)/C(x)

Remainder is not 0: Error has been detected

$\square$  Sender and receiver must use the same C(x)

Examples: Ethernet (CRC-32)

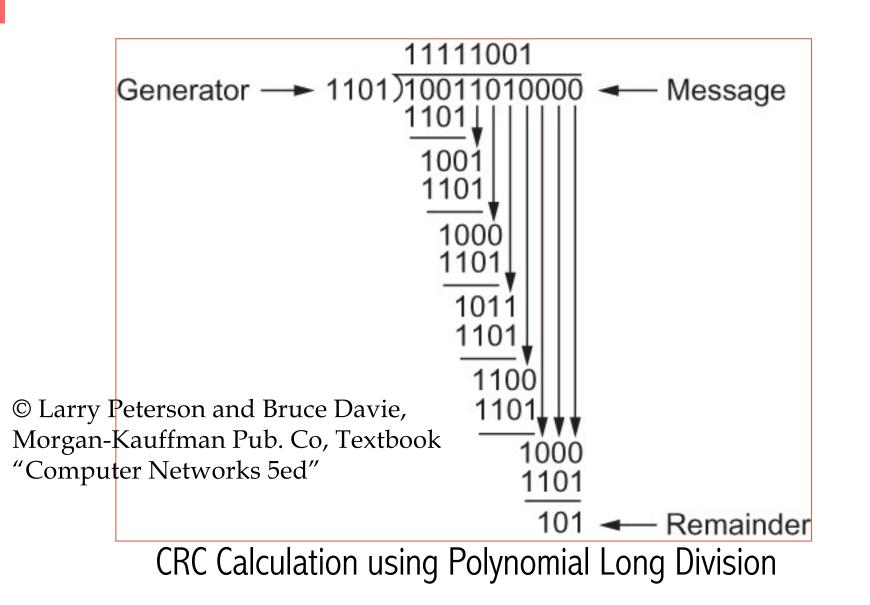

© Larry Peterson and Bruce Davie, Morgan-Kauffman Pub. Co, Textbook

"Computer Networks 5ed"

#### 15

#### Polynomial Arithmetic Modulo 2

- Any polynomial B(x) can be divided by a divisor polynomial C(x) if B(x) is of higher degree than C(x).

- Any polynomial B(x) can be divided once by a divisor polynomial C(x) if B(x) is of the same degree as C(x).

- The remainder obtained when B(x) is divided by C(x) is obtained by subtracting C(x) from B(x).

- To subtract C(x) from B(x), we simply perform the exclusive-OR (XOR) operation on each pair of matching coefficients.

17

### Properties of Generator Polynomial

- In general, it is possible to prove that the following types of errors can be detected by a C(x) with the stated properties

- All single-bit errors, as long as the xk and x0 terms have nonzero coefficients.

- All double-bit errors, as long as C(x) has a factor with at least three terms.

- Any odd number of errors, as long as C(x) contains the factor (x+1).

- Any "burst" error (i.e., sequence of consecutive error bits) for which the length of the burst is <u>less than k bits</u>. (Most burst errors of larger than k bits can also be detected.)

18

- Six generator polynomials that have become international standards are:

- **CRC-8** =  $x^8 + x^2 + x + 1$

- $\square CRC-10 = x^{10}+x^9+x^5+x^4+x+1$

- **CRC-12** =  $x^{12}+x^{11}+x^3+x^2+x+1$

- **CRC-16** =  $x^{16}+x^{15}+x^2+1$

- **CRC-CCITT** =  $x^{16}+x^{12}+x^{5}+1$

- CRC-32 =  $x^{32}+x^{26}+x^{23}+x^{22}+x^{16}+x^{12}+x^{11}+x^{10}+x^8+x^7+x^5+x^4+x^2+x+1$

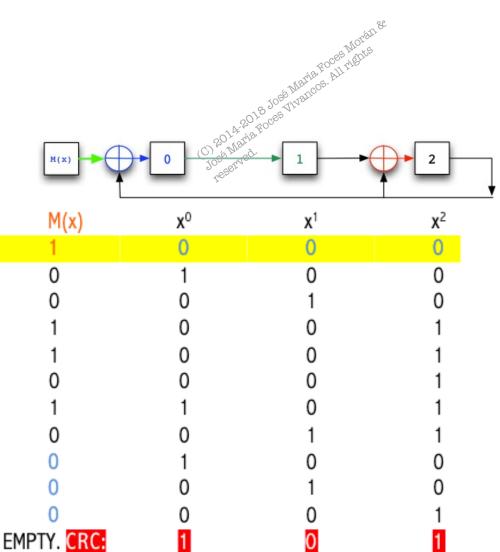

#### Steps to compute the CRC by shift registers 1/4 (Example from pg 101/102 of P&D textbook)

#### Complementary notes to CRC computing by shift registers ©2013, José María Foces Morán

1. Generator polynomial of CRC example in pg. 101 and 102 of P&D textbook.

$C(x) = 1 + x^{2} + x^{3} = 1 \cdot x^{0} + 0 \cdot x^{1} + 1 \cdot x^{2} + 1 \cdot x^{3}$

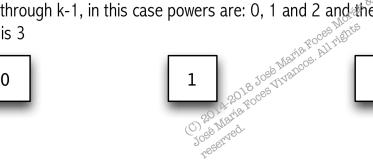

2. One-bit shift registers

The order of C(x) is k = 3, the circuit will have k registers, each assigned to powers of x 0 through k-1, in this case powers are: 0, 1 and 2 and the number of shift registers is 3

# Computing CRC by shift registers 2/4 (Example from pg 101/102 of P&D textbook)

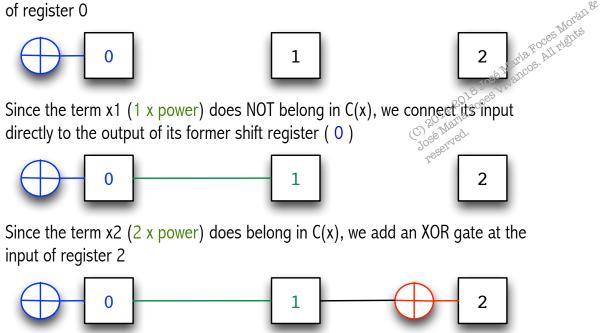

$$C(x) = 1 + x^{2} + x^{3} = 1 \cdot x^{0} + 0 \cdot x^{1} + 1 \cdot x^{2} + 1 \cdot x^{3}$$

3. XOR gate at the input of each register that does belong in C(x) Since the term 1 (0 x power) does belong in C(x), we add an XOR gate at the input of register 0

# Computing CRC by shift registers 3/4 (Example from pg 101/102 of P&D textbook)

#### $C(x) = 1 + x^{2} + x^{3} = 1 \cdot x^{0} + 0 \cdot x^{1} + 1 \cdot x^{2} + 1 \cdot x^{3}$

4. Connect the output of the Most Significant Register (2) to all the XOR gates

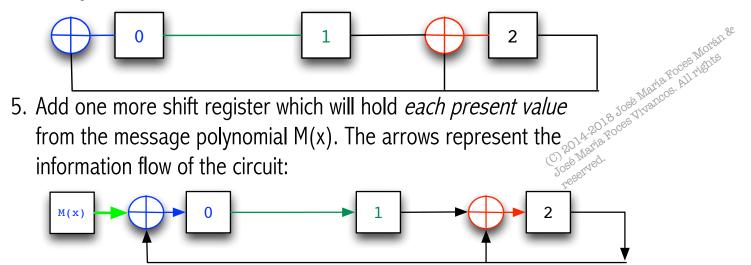

# Computing CRC by shift registers 4/4 (Example from pg 101/102 of P&D textbook)

22

$C(x) = 1 + x^{2} + x^{3} = 1 \cdot x^{0} + 0 \cdot x^{1} + 1 \cdot x^{2} + 1 \cdot x^{3}$

6. The CRC circuit is ready for computing the CRC. This type of circuit computes its next state by using its present state. Initially, the present state of the circuit will be represented by a 0 in each register, except for M(x) which will contain the bits from the message polynomial, starting with its Most Significant Bit — make sure you add k 0's to the least significant bits of M(x), in this case 3. We will represent this computation in tabular form. We proceed by starting with the first row (initial state) and compute the next x<sup>0</sup> bit (next row) according to the circuit and do the same for x<sup>1</sup> and x<sup>2</sup>. When a new row has been computed, we have a new present state and proceed by computing the next state(next row) using the explained procedure. The algorithm finishes when there remain no more bits in M(x), at that state, bits x<sup>0</sup>, x<sup>1</sup>, x<sup>2</sup> contain the CRC.